Fitness Smartwatch Fitness Smartwatch everyone enjoys luck , http://www.eeluckwatch.com Micron Technology today said that it is working with the standardization organization JEDEC to strive for standardization of 3D memory stack packaging technology, and may become the basic manufacturing technology for the next generation of DDR4 memory.

Micron Technology today said that it is working with the standardization organization JEDEC to strive for standardization of 3D memory stack packaging technology, and may become the basic manufacturing technology for the next generation of DDR4 memory.

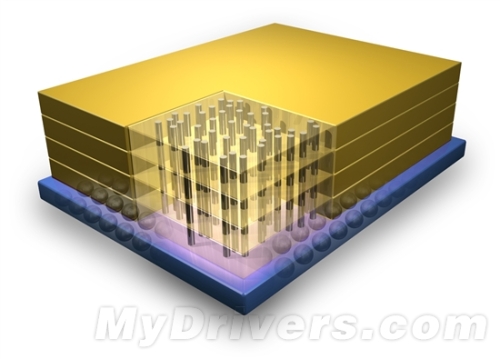

Micron called this standard proposal "3DS" -- not Nintendo's new handheld, but three-dimensional stacking. Micron plans to use a specially designed master-slave DRAM die, where only the main die will be in touch with the external memory controller, from the die is just a younger brother, but also use the optimized DRAM die, a single DLL per stack, reduce the active logic Circuits, shared external I/O, improved timing, reduced external loads, etc. The ultimate goal is to improve memory timing, bus speed, and signal integrity on the one hand, and to reduce power consumption and system stress on the memory subsystem on the other hand.

Micron also specifically demonstrated the timing limitations of current memory technology when reading between different ranks. Due to system limitations, a cycle lag occurs on the data bus, which in turn affects the overall system bandwidth. Micron claims that 3DS technology can eliminate these limitations, and in particular, can accept read instructions from different ranks, thereby "improving data bus utilization and bandwidth."

Prior to this, Micron has used the IBM 32nm HKMG process to mass produce 3D TSV TSVs.